[1]LIU Peihua,LU Huaxiang,GONG Guoliang,et al.Design of an FPGAbased doubleprecision floatingpoint matrix multiplier with pipeline architecture[J].CAAI Transactions on Intelligent Systems,2012,7(4):302-306.

Copy

Design of an FPGAbased doubleprecision floatingpoint matrix multiplier with pipeline architecture

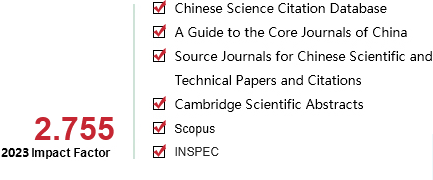

CAAI Transactions on Intelligent Systems[ISSN 1673-4785/CN 23-1538/TP] Volume:

7

Number of periods:

2012 4

Page number:

302-306

Column:

学术论文—智能系统

Public date:

2012-08-25

- Title:

- Design of an FPGAbased doubleprecision floatingpoint matrix multiplier with pipeline architecture

- Keywords:

- matrix multiplication; FPGA; loop pipeline; Cslow retiming; multiplia design

- CLC:

- TP332.2

- DOI:

- -

- Abstract:

- Many application areas, such as digital communication and image processing, make extensive use of matrix multiplication operations, and the computational performance of this operation is critical for the whole system. A parallel doubleprecision floatingpoint matrix multiplier with pipeline architecture was designed to improve the computational performance. The design was implemented in a Xilinx Virtex5 LX155 field programmable gate array (FPGA). Up to 10 processing elements were integrated in a single FPGA device, and they were arranged as an array to achieve parallel computation. The processing elements employed pipelined architecture to increase the speed, and Cslow retiming was applied to solve the datarelated conflicts issues on the loop pipeline. The postRoute simulation results show that the peak performance of the matrix multiplier can achieve 5 000 MFLOPS. In addition, the matrix multiplication experiments with different dimensions were carried out, and the results confirm that the design achieved high computational performance.

- References:

-

[1]AMIRA A, BENSAALI F. An FPGA based parameterizable system for matrix product implementation[C]//IEEE Workshop on Signal Processing Systems (SPIS’02). San Diego, 2002: 7579.

[2]JANG J, CHOI S, PRASANNA V K K. Area and time efficient implementations of matrix multiplication on FPGAs[C]//2002 IEEE International Conference on Field Programmable Technology. Seoul, Korea, 2002: 93100.

[3]CAMPBELL S J, KHATRI S P. Resource and delay efficient matrix multiplication using newer FPGA devices[C]//Proceedings of the 16th ACM Great Lakes Symposium on VLSI. Philadelphia, USA, 2006: 308311.

[4]田翔,周凡. 基于FPGA的实时双精度浮点矩阵乘法器设计[J]. 浙江大学学报: 工学版, 2008, 42(9): 16111615.

TIAN Xiang, ZHOU Fan. Design of field programmable gate array based realtime double precision floatingpoint matrix multiplier[J]. Journal of Zhejiang University: Engineering Science, 2008, 42(9): 16111615.

[5]LEISERSON C, ROSE F, SAXE J. Optimizing synchronous circuitry by retiming[C]//Proceedings of the 3rd Caltech Conference On VLSI. Rockville, Maryland, 1983: 87116.

[6]SU Ming, ZHOU Lili. Maximizing the throughputarea efficiency of fullyparallel lowdensity paritycheck decoding with Cslow retiming and asynchronous deep pipelining[C]//The 25th International Conference on Computer Design. Washington, DC, USA, 2007: 93100.

[7]肖宇, 王建业, 张伟. 基于IP核的数选式浮点矩阵相乘设计[J]. 集成电路应用, 2011, 37(6): 5255.

XIAO Yu, WANG Jianye, ZHANG Wei. Floatingpoint matrix multiplication design based on IP core[J]. Application of Integrated Circuits, 2011, 37(6): 5255.

[8]许芳, 席毅, 陈虹. 基于FPGA NiosⅡ的矩阵运算硬件加速器设计[J]. 电子测量与仪器学报, 2011, 25(4): 376383.

XU Fang, XI Yi, CHEN Hong. Design and implementation of matrix hardware acceleration based on FPGA/NiosII[J], Journal of Electronic Measurement and Instrument, 2011, 25(4): 376383.

[9]黎铁军, 李秋亮, 徐炜遐. 一种128位高性能全流水浮点乘加部件[J]. 国防科技大学学报, 2010, 32(2): 5660.

LI Tiejun, LI Qiuliang, XU Weixia. A high performance pipeline architecture of 128 bit floatingpoint fused multiply add unit[J].Journal of National University of Defense Technology, 2010, 32(2): 5660.

- Similar References:

Memo

-

Last Update:

2012-09-26