[1]ZHANG Chao,LIU Zheng,ZHAO Wei.Hardware evolution based on a new chromosome encoding method[J].CAAI Transactions on Intelligent Systems,2011,6(5):450-455.

Copy

Hardware evolution based on a new chromosome encoding method

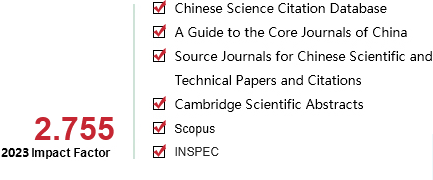

CAAI Transactions on Intelligent Systems[ISSN 1673-4785/CN 23-1538/TP] Volume:

6

Number of periods:

2011 5

Page number:

450-455

Column:

学术论文—人工智能基础

Public date:

2011-10-30

- Title:

- Hardware evolution based on a new chromosome encoding method

- Keywords:

- hardware evolution; chromosome encoding; field programmable logic array(FPLA); Verilog HDL

- CLC:

- TP18;TP302.8

- DOI:

- -

- Abstract:

- This paper proposed an FPLAbased chromosome encoding approach and a parallel hardware evolution method on the basis of a new encoding approach. The ANDORNOT gates are the basic units of the chromosome, so by decomposing the chromosome while evolving and integrating it when computing the adaptation, the evolution time can be shortened. This benefits the evolution of massive and complex circuits. Taking the circuit of changing 4 bits binary code to gray code as an example, the result shows that the average speed increases 32.25 percent over 20 evolutions when using the proposed method. In order to facilitate intrinsic evolutions, the C program was also exploited for translating the chromosome to Verilog hardware language. The encoding method was able to handle multiinput and multioutput circuit evolution, and the chromosome’s length was variable. According to the evolution of the heterogeneous circuits based on this feature, fault tolerance was achieved. This work is significant for online repair used to improve the reliability of electronic systems exposed to harsh space environments.

- References:

-

[1]王友仁,姚睿,朱开阳,等.仿生硬件理论与技术的研究现状与发展趋势分析[J].中国科学基金, 2004, 18(5): 273277.

WANG Youren, YAO Rui, ZHU Kaiyang, et al. The present state and future trends in bioinspired hardware research[J]. Bulletin of National Science Foundation of China, 2004, 18(5): 273277.

[2]XIN Y, HUGICHI T. Promises and challenges of evolvable hardware[J]. IEEE Transactions on Systems, Man, and Cybernetics—Part C: Applications and Reviews, 1999, 29(1): 8797.

[3]TORRESEN J. A divideandconquer approach to evolvable hardware[C]//Proceedings of the Second International Conference on Evolvable Systems: From Biology to Hardware (ICES’98). London, UK: SpringerVerlag, 1998: 5765.

[4]KALGANOVA T. Bidirectional incremental evolution in extrinsic evolvable hardware[C]//Proceedings of the Second NASA/DOD Workshop on Evolvable Hardware (EH’00). Washington, DC, USA: IEEE Computer Society, 2000: 6574.

[5]JACKSON D. Partitioned incremental evolution of hardware using genetic programming[C]//Proceedings of the 11th European Conference on Genetic Programming. Berlin, Germany: SpringerVerlag, 2008: 8697.

[6]Xilinx Inc. Two flows for partial reconfiguration: modulebased or difference based[EB/OL]. [20100511]. http: //www. xilinx. com /support/documentation/application_notes/xapp290. pdf.

[7]原亮,丁国良,褚杰,等.EHW实现过程中VHDL程序自动生成研究[J].军械工程学院学报, 2008, 20(4): 6669.

YUAN Liang, DING Guoliang, CHU Jie, et al. Automatic making of VHDL program for EHW processing[J]. Journal of Ordnance Engineering College, 2008, 20(4): 6669.

[8]姚爱红,张国印,关琳.基于动态可重构FPGA的自演化硬件概述[J].智能系统学报, 2008, 3(5): 436442.

YAO Aihong, ZHANG Guoyin, GUAN Lin. A survey of dynamically and partially reconfigurable FPGAbased selfevolvable hardware[J]. CAAI Transactions on Intelligent Systems, 2008, 3(5): 436442.

[9]姚睿,王友仁,于盛林,等.具有在线〖CM4*2/3-4〗修复能力的强容错三模冗余系统设计及实验研究[J].电子学报, 2010, 38(1): 177183.

?YAO Rui, WANG Youren, YU Shenglin, et al. Design and experiments of enhanced faulttolerant triplemodule redundancy systems capable of online selfrepairing[J]. Acta Electronica Sinica, 2010, 38(1): 177183.

- Similar References:

Memo

-

Last Update:

2011-11-16