[1]YAO Ai-hong,ZHANG Guo-yin,GUAN L in.A survey of dynam ically and partially reconf igurable FPGA-based self-evolvable hardware[J].CAAI Transactions on Intelligent Systems,2008,3(5):436-442.

Copy

A survey of dynam ically and partially reconf igurable FPGA-based self-evolvable hardware

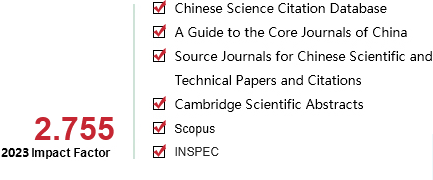

CAAI Transactions on Intelligent Systems[ISSN 1673-4785/CN 23-1538/TP] Volume:

3

Number of periods:

2008 5

Page number:

436-442

Column:

综述

Public date:

2008-10-25

- Title:

- A survey of dynam ically and partially reconf igurable FPGA-based self-evolvable hardware

- CLC:

- TP303

- DOI:

- -

- Abstract:

- The objective of evolvable hardware (EHW) research is the development of automated electronic2circuit design, or a system capable of adap tive alterations to the hardware of its structure. EHW has a great variety of ap2 p lications in fields such as design automation, controllers for autonomous mobile robots, and wireless sensor net2 work nodes. Self2evolutionary hardware comp letes genetic operations and the evaluation of fitness in an on2chip mi2 crop rocessor. The on2chip microp rocessor core of the dynamically and partially reconfigurable field2p rogrammable gate array ( FPGA) runs the genetic algorithm, simulates the evolving p rocess to search for possible circuits, and then sets the on2chip reconfigurable logic so that it runs designswhich are superior to the originalman2made ones, or are op timal designs. In thisway adap tive hardware is possible. When a circuit fails, the self2evolutionary hard2 ware can automatically search for new configurations, using the abundant resources on the chip to rep lace the failed area, realizing the goal of self2repairing hardware. In this paper, the ideas behind self2EHW research, the archi2 tecture of self2EHW and the latest p rogress in the area are studied. The p rimary p roblems to be solved are then summarized. Finally, future research directions are pointed out, such as ways to establish a highly efficient map2 p ing mode between chromosomal encoding of circuits and the configuration bit strings of reconfigurable logic.

- References:

-

[ 1 ]YAO X, H IGU ICH I T. Promises and challenges of evolvab2 le hardware[ J ]. IEEE Trans on SystemsMan and Cybernet2 ics, 1999, 29 (1) : 87297.

?[ 2 ]BENTLEY P, GORDON T, KIM J , et al. New trends in evolutionary computation[C ] / / Proc 2001 Congress on Evo2 lutionary Computation. Seoul, South Korea, 2001: 1622 169.

[ 3 ]LOHN J , HORNBY G. Evolvable hardware: using evolu2 tionary computation to design and op timize hardware systems [ J ]. IEEE Computational Intelligence Magazine, 2006, 1 (1) : 19227.

[ 4 ] THOMPSON A, LAYZELL P, ZEBULUM R S. Exp lora2 tions in design space: unconventional electronics design through artificial evolution[ J ]. IEEE Trans on Evolutionary Computation, 1999, 3 (3) : 1672196.

[ 5 ] SUBB IAH P, RAMAMURTHY B. The study of fault toler2 ant system design using comp lete evolution hardware [ C ] / / Proc 2005 IEEE International Conference on Granular Com2 puting. Beijing, China, 2005: 6422645.

[ 6 ] STEFATOS E, ARSLAN T. An efficient fault2tolerantVLSI architecture using parallel evolvable hardware technology [ C ] / /Proc 2004 NASA /DoD Conference on Evolvable Hardware. Seattle, USA, 2004: 972103.

?[ 7 ]UPEGU IA, SANCHEZ E. Evolving hardware by dynami2 cally reconfiguring Xilinx FPGA [C ] / /Proc the International Conference on Evolvable Systems ( ICES ). Barcelona, Spain, 2005: 56265.

[ 8 ]RESANO J , MOZOS D, VERKEST D, et al. A reconfigu2 ration manager for dynamically reconfigurable hardware[ J ]. IEEE Trans on Design & Test of Computers, 2005, 22 (5) : 4522460.

[ 9 ] SAPARGAL IYEV Y, KALGANOVA T. Absolutely free ex2 trinsic evolution of passive low2pass filter [ C ] / /Canadian Conference on Electrical and Computer Engineering. Otta2 wa, Canada, 2006: 121021213.

?[ 10 ]ZHANG Y, SM ITH S, TYRRELL A. Digital circuit design using intrinsic evolvable hardware[C ] / /Proc 2004 NASA / DoD Conference on Evolvable Hardware. Krakow, Port2 land, 2004: 55262.

[ 11 ] TUFTE G, HADDOW P. Biologically2insp ired: a rule2 based self2reconfiguration of a virtex chip [ C ] / /Proc the Computational Science ( ICCS). Krakow, Poland, 2004: 124921256.

?[ 12 ]MORENO J , SANCHEZ E, CABESTANY J. An in2system routing strategy for evolvable hardware p rogrammable p lat2 forms[C ] / /Proc the 3 rd NASA /DoD. Long Beach: IEEE Computer Society Press, 2001: 1572166.

[ 13 ]EVANS J , ARSLAN T. The imp lementation of an evolvab2 le hardware system for real time image registration on a system2on2chip p latform[C ] / /Proc 2002 NASA /DoD Con2 ference on Evolvable Hardware. Alexandria, Virginia, 2002: 1422146.

[14 ]赵曙光, 杨万海. 一种用于演化硬件的染色体编码新方法[ J ]. 西安电子科技大学学报, 2000, 27 (6) : 7782 780.

ZHAO Shuguang, YANGWanhai. A new method for the chromosome rep resentation in the evolvable hardware [ J ]. Journal of Xidian University, 2000, 27 (6) : 7782780.

?[ 15 ]Xilinx Inc. Virtex2II p latform FPGA user guide[ EB /OL ]. [ 2005203224 ]. http: / /china. xilinx. com / support/docu2 mentation /user_guides/ug002. pdf.

[ 16 ]康立山, 何 魏, 陈毓屏. 用函数型可编程器件实现演化硬件[ J ]. 计算机学报, 1999, 22 (7) : 7812784.

KANG L ishan, HEWei, CHEN Yup ing. Evolvable hard2 ware realized with function type p rogrammable device [ J ]. Chinese Journal of Computers, 1999, 22 (7) : 7812784.

[ 17 ] L IU H, M ILLER J , TYRRELL A. Intrinsic evolvable hardware imp lementation of a robust biological develop2 ment model for digital systems [ C ] / /Proc 2005 NASA / DoD Conference on Evolvable Hardware. Washington D C, 2005: 87292.

?[ 18 ]LEV I D, GUCCIONE S. Evolvable genetic FPGA: evol2 ving stable circuits on mainstream FPGA devices Hardware [ C ] / /Proc the 1 st NASA /DoD. Pasadena, USA, 1999: 12217.

?[ 19 ]Xilinx Inc. Two flows for partial reconfiguration: Module based or difference based [ EB /OL ]. [ 2004209211 ]. ht2 tp: / /www. xilinx. com / support/documentation / app lication _notes/xapp290. pdf.

[ 20 ] SANTIN I C, AMARAL J , PACHECOM, et al. Evolution2 ary analog circuit design on a p rogrammable analog multi2 p lexer array [ C ] / /Proc IEEE International Conference on Field2Programmable Technology ( FPT2002 ). HongKong, China, 2002: 189-196.

[ 21 ] SIPPER M, SANCHEZ E, MANGE D, et al. The POE Model of bio2insp ired hardware systems: a short introduc2 tion[C ] / /Proc the Second Annual Conference of Genetic Programming. Stanford, USA, 1997: 5102511.

[ 22 ]OREIFEJ R, AlHADDAD R, HENG T, et al. Layered app roach to intrinsic evolvable hardware using direct bits2 tream manipulation of virtex II p ro devices [ C ] / / Interna2 tional Conference on Field Programmable Logic and App li2 cations( FPL 2007). Amsterdam, 2007: 2992304.

[ 23 ]NASA AMES Research Center. AMES technology capabili2 ties and facilities [ EB /OL ]. [ 2007205229 ]. http: / /www. nasa. gov/ centers/ ames/ research / technology2onepagers/ evolvable_systems. html.

[ 24 ] KAJ ITAN I I, HOSH INO T, IWATA M, et al. Variable length chromosome GA for evolvable hardware [ C ] / /Proc IEEE International Conference on Evolutionary Computa2 tion. Nagoya, Japan, 1996: 4432447.

?[ 25 ] SAKANASH I H, IWATA M, H IGUCH I T. Evolvable hardware for lossless comp ression of very high resolution bi2level images [ C ] / /Proc IEE Computers and Digital Techniques. London, UK, 2004: 2772286.

[ 26 ] LEHRE P, HADDOW P. Developmental mapp ings and phenotyp ic comp lexity [ C ] / /Proc the IEEE Congress on Evolutionary Computation (CEC). Portland, USA, 2003: 62268.

[ 27 ] GARV IE M, THOMPSON A. Evolution of combinatorial and sequential on2line self2diagnosing hardware[C ] / /Proc the 2003 NASA /DoD Conference on Evolvable Hardware. Chicago: IEEE Computer Society Press, 2003: 1672173.

[ 28 ]GAR IS H, KORKIN M, GERS F, et al. ATR’s artificial brain (CAM2brain) p roject: a samp le of what individual CoDi21Bitmodel evolved neural netmodules can do[C ] / / Proc the IEEE Congress on Evolutionary Computation (CEC). Washington,DC,USA, 1999: 197921987.

[ 29 ]AROSTEGU IM, SANCHEZ E, CABESTANY J. An in2 system routing strategy for evolvable hardware p rogramma2 ble p latforms [ C ] / /Proc The Third NASA /DoD. Long Beach, 2001: 1572166.

[ 30 ]GORDON T, BENTLEY P. Development brings scalability to hardware evolution [ C ] / /Proc the 2005 NASA /DoD Conference on Evolvable hardware. Washington,DC,USA, 2005: 2722279.

[ 31 ]GALLAGHER J , V IGRAHAM S, KRAMER G. A family of compact genetic algorithms for intrinsic evolvable hard2 ware [ J ]. IEEE Trans on Evolutionary Computation, 2004, 8 (2) : 1112126.

- Similar References:

Memo

-

Last Update:

2009-05-18