# 基于动态可重构 FPGA的自演化硬件概述

姚爱红,张国印,关 琳

(哈尔滨工程大学 计算机科学与技术学院,黑龙江 哈尔滨 150001)

摘 要:演化硬件研究如何利用遗传算法进行硬件自动设计,或者设计随外界环境变化而自适应地改变自身结构的 硬件,在电子设计自动化、自主移动机器人控制器、无线传感器网络节点等领域都有潜在的应用价值,自演化硬件是 在硬件内部完成遗传操作和适应度计算 ,利用支持动态部分可重构的 FPGA 芯片上的微处理器核实现遗传算法 ,模 拟生物群体演化过程搜索可能的电路设计并配置片上的可重构逻辑,找到最优或较优的设计结果,从而实现自适应 硬件,当电路发生故障时,自演化硬件自动搜索新的配置,利用片上冗余资源取代故障区域,从而实现自修复硬件, 介绍了基于动态部分可重构 FPGA的自演化硬件的基本思想、体系结构以及研究现状,总结并提出了亟待解决的关 键技术,指出高效的电路染色体编码表示与可重构逻辑配置位串之间的映射方式是当前研究的重点之一.

关键词:演化硬件;动态可重构;染色体编码; FPGA

中图分类号: TP303 文献标识码: A 文章编号: 1673-4785 (2008) 05-0436-07

# A survey of dynam ically and partially reconfigurable FPGA-based self-evolvable hardware

YAO Ai-hong, ZHANG Guo-yin, GUAN Lin

(College of Computer Science and Technology, Harbin Engineering University, Harbin 150001, China)

Abstract: The objective of evolvable hardware (EHW) research is the development of automated electronic-circuit design, or a system capable of adaptive alterations to the hardware of its structure. EHW has a great variety of applications in fields such as design automation, controllers for autonomous mobile robots, and wireless sensor network nodes Self-evolutionary hardware completes genetic operations and the evaluation of fitness in an on-chip microp rocessor. The on-chip microp rocessor core of the dynamically and partially reconfigurable field-programmable gate array (FPGA) runs the genetic algorithm, simulates the evolving process to search for possible circuits, and then sets the on-chip reconfigurable logic so that it runs designs which are superior to the original man-made ones, or are optimal designs In this way adaptive hardware is possible. When a circuit fails, the self-evolutionary hardware can automatically search for new configurations, using the abundant resources on the chip to replace the failed area, realizing the goal of self-repairing hardware. In this paper, the ideas behind self-EHW research, the architecture of self-EHW and the latest progress in the area are studied. The primary problems to be solved are then summarized Finally, future research directions are pointed out, such as ways to establish a highly efficient mapping mode between chromosomal encoding of circuits and the configuration bit strings of reconfigurable logic.

Keywords: evolvable hardware; dynamical reconfiguration; chromosome encoding; FPGA

随半导体工艺水平的迅速提高 ,单个芯片所能 提供的晶体管数目达到十亿量级,基于电子设计自 动化 (electronic design automation, EDA)软件工具 的传统设计方法的设计能力与芯片集成度之间的差

距越来越大.演化硬件(evolvable hardware, EHW) 利用硬件自身的快速并行计算能力在可能的设计空 间进行搜索,从而实现硬件的自动设计,成为计算机 系统结构和电子设计自动化领域的研究热点之 一[13]. 利用演化算法 (evolutionary algorithm, EA)在 传统设计空间内进行搜索,有可能找到比手工设计

收稿日期: 2007-06-19.

通信作者:姚爱红. E-mail: yaoaihong@hrbeu edu cn

更优的结果;而如果在传统设计空间之外搜索,则有可能发现传统设计技术无法解决的问题的答案<sup>[4]</sup>. 广义上的演化硬件不仅包括能够利用演化算法进行电路自动设计的硬件,还包括自适应型传感器以及能够适应变化的环境、并且在运行期间增强性能或进行自我修复的整个演化系统<sup>[5-6]</sup>.

演化硬件主要由演化算法及可重构模拟或数字阵列组成,例如由遗传算法(genetic algorithm, GA)与现场可编程门阵列(field programmable gate array, FPGA)构成.目前,在利用 FPGA和 GA进行电路的演化设计这一方面,演化设计的流程与常规的遗传算法流程相似[7],包括染色体编码、种群初始化、适应度评估、遗传操作(选择、交叉、变异)等步骤的迭代.所不同的是,个体的适应度是通过将个体(配置位串)实际加载到 FPGA上,再按照测试集逐项实际测试而得到,而演化的目标是找到一个完全符合要求的个体(适应度等于 100%).在演化成功之后,将成熟染色体转换成对应的 FPGA 配置位串,即可得到指定功能的硬件电路.

自演化硬件是在硬件内部完成遗传操作和适应度计算<sup>[89]</sup>,例如,在 Xilinx Virtex II Pro FPGA上利用片上的 Power PC微处理器硬核实现遗传算法,在同一片 FPGA上演化生成电路<sup>[10-11]</sup>.基于可在运行时动态部分重构的 FPGA,利用其片上集成的微处理器核执行演化算法,结合快速动态重构技术将生成的染色体位串配置片上的可重构部分,实现适应度实时在线评估,对于实现自修复硬件和自适应硬件都具有重要的意义.

## 1 自演化硬件结构及分类

通常情况下,FPGA 重构时不能改变连线资源的分配,而重构所需的电路配置信息在系统运行过程中动态产生. 重构时系统可以不暂停,边重构边工作<sup>[8,12]</sup>. 这种重构系统设计复杂,但灵活性大,能充分发挥出硬件运算的效率,较适合应用于高速数字滤波器、演化计算、定制计算等方面. 随着可编程器件容量的增大,高集成度的 FPGA 可以将整个系统集成在单个可编程器件上,构成单芯片可重构系统<sup>[13]</sup>(system on a programmable chip, SoPC). SoPC可包含多个处理器、DSP、高速总线、内存、外围组件和各种不同的专用标准器件,各部件之间可以分别通过高速数据通路连接. 这种系统中,处理器和可重构逻辑是紧密耦合的结构,同时,利用片上存储系统

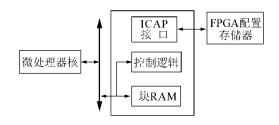

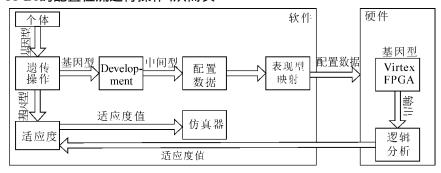

和处理器与可重构逻辑的高速接口可以实现自重构平台.一种典型的自演化硬件体系结构如图 1所示<sup>[7]</sup>.片上微处理器核执行演化算法生成新的配置位串,通过片上高速总线对可重构逻辑(块 RAM)进行动态配置,初始配置信息可以通过配置存储器加载,演化结束后生成的配置位串也可以保存到配置存储器中.

图 1 自演化硬件体系结构

Fig 1 Self-evolvable-hardware architecture

根据染色体编码方式、演化过程、芯片种类不同,可以对演化硬件进行如下分类.

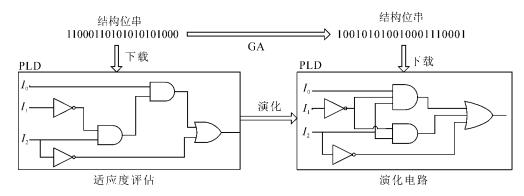

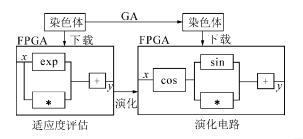

按照演化硬件时使用的染色体表示方式可分为 直接编码方式和间接编码方式,直接方式即直接将 FPGA的配置位串作为染色体,在评估和对可编程 逻辑电路进行配置时可直接将染色体下载到 FPGA 中.直接编码方式通过直接对 FPGA 的配置位串进 行演化,以改变门级电路的连接,如图 2所示为最小 项编码方式对可编程逻辑器件 (programmable logic device, PLD)的配置位串进行直接演化[14]. 由于 FP-GA的配置位串很长[15](根据电路规模通常在几万 位到几十万位之间),若直接将整个配置位串作为 染色体进行编码,则由于染色体长,演化过程所需的 存储和运算量过大,直接限制了演化的速度和所能 处理的电路规模,间接编码方式将电路更高层次的 表达方式 (树或语法等)作为染色体,在评估和对电 路配置时需要经过翻译过程,生成配置位串,间接编 码方式采用抽象的表达方式,即用树或者语法规则 产生电路. 例如,染色体为按规则产生的衍生树 (derivation tree),树的所有可能结果与电路结构的 所有可能结果——对应. 函数型演化硬件如图 3所 示[16],其演化的基本元素不是门电路,而是基本的 功能模块,如加、减模块等.这样既可以获得更为复 杂功能的电路,又不增加演化的困难.但是函数型演 化需要新型的函数级可编程逻辑器件(functional FPGA, FFPGA)的支持.

图 2 直接演化方式

Fig 2 Direct evolving mode

图 3 函数型演化方式

Fig 3 Extrinsic functional evolving mode

按照硬件演化的过程不同可分为外部演化硬件(extrinsic EHW)、内部演化硬件(intrinsic EHW)以及自演化硬件(complete EHW 或者 self-EHW),外部演化方式的适应度评估基于电路模型和软件仿真,其运算量较大、耗时多,但不受特定实验平台的限制,因而更灵活,演化的结果也更具普遍意义,多与间接编码方式配合用于模拟电路的演化设计;内部演化方式的适应度评估基于实际的电路配置和测试,其演化速度较快且可利用器件的物理特性(温度、功耗、局部故障等),在数字电路的演化设计中被广泛采用[17];高端 FPGA片上往往集成一个或多个微处理器核,利用其片上的处理器执行演化算法并进行动态调度配置即构成自演化硬件。

实现演化硬件的芯片可分为商业 FPGA芯片和专用演化芯片[18].商业 FPGA芯片的内部结构不公开,不能接收随机配置位串[19],重构过程依赖于厂商提供的软件工具,这些因素限制了基于商业 FPGA芯片的演化硬件研究.基于商业 FPGA进行内部演化,需要利用厂商提供的工具软件对演化产生的随机配置位串加以过滤,只将 FPGA内部结构允许的配置位串用于 FPGA的配置以避免不合法的配置损坏器件,保证演化设计结果的可重复性和鲁棒性.模拟电路的演化大多采用自制的由分立元器件组成

的实验平台,有些研究者则使用了可编程模拟器件,如现场可编程模拟阵列<sup>[20]</sup>.近年来,针对 EHW 研究的特殊需要研制适用的专用集成电路芯片已成为提高内部演化效率和 EHW 实用化程度的重要途径.

### 2 研究现状

演化硬件属于仿生硬件研究的一个分支,因而根据生物体产生和发展的自然规律,可以从种群发生学(phylogeny)、个体发生学(ontogeny)以及后天遗传学(epigenesis)3个层次建立仿生硬件体系的POE模型 $^{[21]}$ .以 P (phylogeny)轴代表像演化硬件这类模拟群体演化过程的仿生硬件系统,以 O (ontogeny)轴代表像胚胎型仿生硬件这类模拟多细胞组织生长过程的仿生硬件系统,以 E (epigenesis)轴代表像人工神经网络计算机等模拟神经系统、免疫系统和内分泌系统,通过与外部环境相互作用进行自学习的仿生硬件系统。在此框架下,可以在 PE平面、OE平面、PO 平面甚至 POE空间确立仿生硬件系统的发展方向。

目前全球以美国国家宇航局和欧洲空间局为代表的多家研究机构在进行演化硬件方面的研究,并取得了一些研究成果,主要分为演化硬件的实用性研究和演化硬件理论研究 2个方面.演化硬件实用性研究方面,美国国家宇航局、日本和主要的 FPGA厂商在各自领域开展了相应的研究.演化硬件理论研究主要集中在染色体编码表示与电路之间的映射关系的研究和基因编码复杂性研究等几个方面[22].

美国国家宇航局 Ames研究中心主要研究用于航天飞机、宇宙飞船电子系统的自修复硬件或进行硬件的自动设计<sup>[23]</sup>. 当飞行器穿越高电离辐射区域时,敏感元件(例如 FPGA)可能会发生故障,一旦检测到某个 FPGA芯片故障,自修复硬件系统立即运

行演化算法利用片上冗余资源重新配置,直至功能恢复.在硬件自动设计方面,2005年该中心成功地应用遗传算法、遗传程序设计、模拟退火算法等混合启发式算法实现了美国 ST-5微小卫星系统的天线设计,演化产生的设计结果与手工设计相当,甚至在某些方面(质量、成本)超过了手工设计.日本Tsukuba大学的 T. Higuchi等人在演化硬件芯片的工业化应用研究上取得了成绩[24-25].他所在的研究小组研究了利用可变长度染色体演化硬件实现手写输入的模式识别系统中的模式分类器,该演化硬件平台由 4块 Xilinx XC4025芯片构成可重构逻辑部

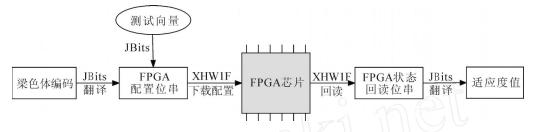

分,遗传操作由计算机完成,演化过程结束后将选中的染色体位串下载至 FPGA中,该系统属于外部演化硬件. Xilinx公司的 D. Levi等人设计了支持在商业 FPGA 芯片上进行演化的软件工具链 [18],包括GeneticFPGA、JB its和 XHW IF (xilinx hardware interface)接口. 其演化过程如图 4所示,当前种群中的每一个染色体经过 JB its转换为合法的配置位串并加入相应的测试向量形成配置信息,通过 XHW IF接口下载到 FPGA 芯片中,经过规定时间后再通过XHW IF接口回读 FPGA 内部状态位串,由 JB its转换后就得到了该染色体的适应度值.

图 4 GeneticFGPA演化过程

Fig 4 Evolving process of geneticFPGA

挪威科技大学的 P. Haddow 等人对基因编码的 Lempel-Ziv复杂性进行了讨论[10,26],研究结果表明根 据 LZ复杂性理论, 当基因编码为随机位串时, 其可 压缩性几乎为零:而真正的电路编码是具有一定的规 律性的位串,因此可以进行压缩,LZ复杂性给出了位 串可压缩率的上边界,缩短位串长度,不仅可以节省 存储空间和减少遗传操作的计算量,同时还缩小了最 优搜索的解空间,加快了演化过程.英国 Sussex大学 的 A. Thomp son等人在硬件内部演化技术上取得了 进展[27],研究极小规模电子电路的演化,其研究被证 明符合摩尔定理.这种极小规模电子电路甚至小到只 包含一个单一的晶体管. 原美国尤他州立大学的 H. de Gari 等人曾经对大规模硬件演化平台 CBM (CAM B rains Machine)展开研究, CBM 包含 72片 FPGA芯片(Xilinx XC6264),计划模拟人脑的部分学 习功能[28].

最近几年,国内少数单位的研究人员对演化硬件进行了研究,并在可自修复的演化硬件研究上取得了一些研究成果.但大多数研究内容侧重于演化算法、采用外部演化方式的函数级数字电路的演化<sup>[16]</sup>.采用的演化芯片集成度小,如 GAL (gate array logic)芯片,开展演化硬件应用基础研究不够,还没有成功应用的报道.目前对模拟系统硬件演化技术研究还很少,缺少专门进行演化硬件研究的学术群体.

#### 3 亟待解决的关键技术

演化硬件虽然是一个比较新的研究领域,但是由于其发展与可编程逻辑器件的结构密切相关,因而随着支持动态部分重构 FPGA 器件不断更新,硬件特性的不断改变,一些早期的演化硬件技术现在已不再适用.另外,由于演化硬件对于使用者是一个黑盒,因而不能随电路种类和规模扩大而对原有的设计进行扩展和升级[28-29],必须要重新开始演化过程,造成了重复和浪费.目前,已经演化成功了一些小规模的数字电路并投入应用,但是对于大规模复杂电路的演化能力有限且缺乏可扩展性.如何找到提高染色体表达有效性的电路表示方法,以及寻求简洁高效的演化算法和评估方法,成为自演化硬件研究中的关键问题.需要在以下几个方面进行更深入地研究:

1)研究适于自演化硬件的电路编码表示方案<sup>[27]</sup>. 染色体直接编码方式由于在演化过程中对存储和计算资源随演化电路规模增长呈指数性增长,因而不适合采用. 染色体间接编码方式虽然简化了染色体表示,但实际上是以增加基因型到表现型映射的复杂性为代价的. 而且,在演化过程中需要通过适应度评估来确定个体的好坏,而间接编码的染色体结构与FPGA的实际配置数据差别很大,并不能直接用作适应度值计算,需要经翻译过程将每个个体转换为相应

的配置位串,然后通过软件模拟或硬件直接配置,对电路的输入向量产生相应的输出并进行适应度计算。目前,在 VirtexII系列 FPGA 上进行的演化都需要 Xilinx公司工具软件的支持,因而无法脱离 PC机或工作站运行,难以应用于自演化系统中.

2)研究适应度实时评估方法. 自演化硬件将每一代种群中的每个染色体位串作为可编程电路的配置信息,通过实际测试电路的输入 输出形成个体适应度值,从而实现适应度的实时在线评估. 如果重构时间过长,自演化将失去意义. 因而,通过深入分析FPGA的配置位串规律性,利用 EA算法内在并行性,在基于支持动态部分重构的 FPGA 中实现适应度的实时计算.

3)研究快速动态部分可重构技术. 动态可重构系统在系统运行时,根据计算任务的需要将时域计算密集型任务映射为空域电路,提高了执行速度,但是重构过程本身需要一定的时间开销,通常为毫秒级到秒级,因此,必须对如何快速实现重构进行深入研究. 快速可重构技术主要有配置预取、配置数据压缩、重定位和碎片整理以及缓存(caching)技术等. 由于在演化运算过程中,相邻 2代种群的染色体是有延续性的,充分利用已有的电路配置和重定位技术,采用基于 Bitstream 差异的动态部分重构方法,可以大大加快系统重构速度. Bitstream 文件是指用户的 RTL级代码(用 HDL语言描述)经 EDA工具综合,布局布线后,最终生成的可下载到 FPGA中的二进制码流文件,它包含的是最直接的电路信息. 基于 Bitstream的技术通过直接对 FPGA的配置位流进行操作,从而实

现对 FPGA内部资源的访问和控制. 通过深入分析 Bitstream,利用 Xilinx提供的 JBits API直接生成位流及进行位流修改. JBits由一系列的 Java类库组成,提供了直接访问 Xilinx FPGA Bitstream 文件的应用程序编程接口 (API). 这些 API包括读取和修改 Bitstream 里面包含的逻辑和布线信息. 这个特性使得实现 FPGA动态重构变为可能. 事实上,用户通过 JBits可以对 FPGA里面的每一个 tile的任意资源进行访问和修改,比如特定 LUT里面的某一位,甚至 Slice之间的内部连线也可以通过这些 API接口进行配置.

4)基于二级映射的演化硬件体系结构研究. 在 基因型平面与表现型平面之间采用中间硬件表示层, 基因型平面的编码只对中间层进行,而表现型平面的 实际 FPGA器件的配置位串是通过中间层进行转换 获得的. 中间硬件层的结构相对简单、规整,因而其染 色体编码表示比直接对 FPGA 配置编码简单,降低了 演化过程中对存储和计算资源的需求. 同时,中间硬 件层屏蔽了底层 FPGA的硬件特性,使得演化设计具 有一定的普适性 (generalization,即设计方法所适用的 条件和环境)和可扩展性[30-31](scalability,即所适用 的电路规模和类型). Arostegui等人提出了采用规整 的功能单元 (functional cell)构成二维可重构平面的 结构[29],功能单元的数量可以任意增加,从而使得演 化设计具有可扩展性. R. DeMara等人采用二级映射 机制实现基因型 表现型映射[22],通过虚拟演化硬件 FPGA (virtual EHW FPGA)实现染色体编码到 FPGA 配置位串的转换,其映射过程如图 5所示.

图 5 基于虚拟演化硬件 FPGA的二级映射示意图

Fig 5 Two-layered mapping virtual EHW FPGA

#### 4 结束语

基于动态部分可重构 FPGA 的自演化硬件中,可重构逻辑电路的配置由片上处理器执行演化算法而动态决定,对于实现自适应、自修复硬件电路都具

有重要的意义. 由于遗传算法不需要设计目标的先验知识,设计者只需要将要实现的功能用设计拟合的方式描述出来,演化的方法 (如遗传算法)产生及演化出一系列 FPGA的配置,最终产生具有所需功能的设计,因此有可能克服现有的 EDA软件限制实

现根据环境变化而自适应变化的硬件电路和能够自动重新配置修复故障的硬件电路.基于 SRAM的 FPGA 平台的自演化硬件,无论是功能块实现的逻辑功能,还是各逻辑块相互之间的连线,都可以被反复重新编程,即硬件电路可以随时根据需要而改变,因而又称为自适应计算(adaptive computing).随着深亚微米 VLS 技术的迅速发展,基于动态部分可重构 FPGA 的自演化硬件将在系统普适性和可扩展性方面不断取得进展.

#### 参考文献:

- [1] YAO X, HIGU ICH I T Promises and challenges of evolvable hardware [J]. IEEE Trans on Systems M an and Cybernetics, 1999, 29 (1): 87-97.

- [2] BENTLEY P, GORDON T, KM J, et al. New trends in evolutionary computation [C] // Proc 2001 Congress on Evolutionary Computation Seoul, South Korea, 2001: 162-169.

- [3] LOHN J, HORNBY G Evolvable hardware: using evolutionary computation to design and optimize hardware systems

[J]. IEEE Computational Intelligence Magazine, 2006, 1

(1): 19-27.

- [4] THOM PSON A, LA YZELL P, ZEBULUM R S Explorations in design space: unconventional electronics design through artificial evolution[J]. IEEE Trans on Evolutionary Computation, 1999, 3(3): 167-196

- [5] SUBB AH P, RAMAMURTHY B. The study of fault tolerant system design using complete evolution hardware [C]// Proc 2005 IEEE International Conference on Granular Computing Beijing, China, 2005: 642-645.

- [6] STEFATOS E, ARSLAN T. An efficient fault-tolerant VLSI architecture using parallel evolvable hardware technology

[C]//Proc 2004 NASA/DoD Conference on Evolvable Hardware Seattle, USA, 2004: 97-103.

- [7] UPEGUIA, SANCHEZ E Evolving hardware by dynamically reconfiguring Xilinx FPGA [C]//Proc the International Conference on Evolvable Systems (ICES). Barcelona, Spain, 2005: 56-65.

- [8] RESANO J, MOZOS D, VERKEST D, et al. A reconfiguration manager for dynamically reconfigurable hardware [J].

IEEE Trans on Design & Test of Computers, 2005, 22 (5): 452-460.

- [9] SA PAR GAL IYEV Y, KAL GANOVA T. Absolutely free extrinsic evolution of passive low-pass filter [C]//Canadian Conference on Electrical and Computer Engineering Ottawa, Canada, 2006: 1210-1213.

- [10] ZHANG Y, SM IIH S, TYRRELL A. Digital circuit design

- using intrinsic evolvable hardware [C]//Proc 2004 NASA/DoD Conference on Evolvable Hardware Krakow, Portland, 2004: 55-62

- [11] TUFTE G, HADDOW P. B iologically-inspired: a rule-based self-reconfiguration of a virtex chip [C]//Proc the Computational Science (ICCS). Krakow, Poland, 2004: 1249-1256.

- [ 12 ]MORENO J, SANCHEZ E, CABESTANY J. An in-system routing strategy for evolvable hardware programmable platforms[C]//Proc the 3rd NASA/DoD. Long Beach: IEEE Computer Society Press, 2001: 157-166.

- [13] EVANS J, ARSLAN T. The implementation of an evolvable hardware system for real time image registration on a system-on-chip platform [C]//Proc 2002 NASA/DoD Conference on Evolvable Hardware. A lexandria, Virginia, 2002: 142-146.

- [14]赵曙光,杨万海. 一种用于演化硬件的染色体编码新方法 [J]. 西安电子科技大学学报,2000,27(6):778-780

- ZHAO Shuguang, YANG Wanhai A new method for the chromosome representation in the evolvable hardware [J]. Journal of Xidian University, 2000, 27(6): 778-780.

- [15] Xilinx Inc Virtex-II platform FPGA user guide [EB/OL].

[2005-03-24]. http://china xilinx com/support/documentation/user\_guides/ug002 pdf

- [16]康立山,何 魏,陈毓屏. 用函数型可编程器件实现演化硬件 [J]. 计算机学报, 1999, 22(7): 781-784.

KANG Lishan, HE Wei, CHEN Yuping Evolvable hardware realized with function type programmable device [J]. Chinese Journal of Computers, 1999, 22(7): 781-784.

- [17] LU H, M LLER J, TYRRELL A. Intrinsic evolvable hardware implementation of a robust biological development model for digital systems [C]//Proc 2005 NASA/DoD Conference on Evolvable Hardware. Washington D C, 2005: 87-92

- [18] LEVID, GUCCONE S Evolvable genetic FPGA: evolving stable circuits on mainstream FPGA devices Hardware [C]//Proc the 1st NASA/DoD. Pasadena, USA, 1999: 12-17.

- [19] Xilinx Inc Two flows for partial reconfiguration: Module based or difference based [EB/OL]. [2004-09-11]. http://www.xilinx.com/support/documentation/application\_notes/xapp290.pdf

- [20] SANTNIC, AMARAL J, PACHECO M, et al Evolutionary analog circuit design on a programmable analog multiplexer array [C]//Proc IEEE International Conference on Field-Programmable Technology (FPT2002). HongKong, China, 2002: 189-196

- [21] SIPPER M, SANCHEZ E, MANGE D, et al. The POE Model of bio-inspired hardware systems: a short introduction [C]//Proc the Second Annual Conference of Genetic Programming Stanford, USA, 1997: 510-511.

- [22] ORE IFEJ R, A IHADDAD R, HENG T, et al Layered approach to intrinsic evolvable hardware using direct bits-tream manipulation of virtex II pro devices [C]//International Conference on Field Programmable Logic and Applications (FPL 2007). Am sterdam, 2007: 299-304.

- [ 23 ]NA SA AMES Research Center AMES technology capabilities and facilities [ EB /OL ]. [ 2007-05-29 ]. http://www.nasa.gov/centers/ames/research/technology-onepagers/evolvable\_systems.html

- [24] KAJ ITAN I I, HOSH NO T, WATA M, et al Variable length chromosome GA for evolvable hardware [C]//Proc IEEE International Conference on Evolutionary Computation Nagoya, Japan, 1996: 443-447.

- [ 25 ] SAKANASHIH, WATA M, HKUCHIT Evolvable hardware for lossless compression of very high resolution bir-level images [ C ] //Proc IEE Computers and Digital Techniques London, UK, 2004: 277-286

- [26] LEHRE P, HADDOW P. Developmental mappings and phenotypic complexity [C]//Proc the IEEE Congress on Evolutionary Computation (CEC). Portland, USA, 2003: 62-68

- [27] GARV IE M, THOM PSON A. Evolution of combinatorial and sequential on-line self-diagnosing hardware [C] //Proc the 2003 NASA/DoD Conference on Evolvable Hardware Chicago: IEEE Computer Society Press, 2003: 167-173.

- [28] GAR IS H, KORKN M, GERS F, et al. ATR's artificial brain (CAM-brain) project: a sample of what individual CoD i-1B it model evolved neural net modules can do [C]// Proc. the IEEE Congress on Evolutionary Computation (CEC). Washington, DC, USA, 1999: 1979-1987.

- [29] ARO STEGU IM, SANCHEZ E, CABESTANY J. An insystem routing strategy for evolvable hardware programmable platforms [C]//Proc The Third NASA/DoD. Long Beach, 2001: 157-166.

- [30] GORDON T, BENTLEY P. Development brings scalability to hardware evolution [C]//Proc the 2005 NASA/DoD Conference on Evolvable hardware Washington, DC, USA, 2005: 272-279.

- [31] GALLAGHER J, VIGRAHAM S, KRAMER G A family of compact genetic algorithms for intrinsic evolvable hardware [J]. IEEE Trans on Evolutionary Computation, 2004, 8(2): 111-126

#### 作者简介:

姚爱红,女,1972年生,工学博士,副教授,中国电子学会高级会员.主要研究方向为演化计算、嵌入式系统设计、多媒体传感器网络.发表论文 11篇,其中被 EI ISTP检索收录 6篇,出版著作和译著 3部.

张国印,男,1962年生,工学博士,教授,博士生导师.中国计算机学会计算机教育专委会委员、中国电子学会嵌入式系统专家委员会委员、黑龙江省计算机学会理事.主要研究方向为嵌入式系统、智能控制与智能机器人、网络与

信息安全. 获部级科技进步一等奖 1项、二等奖 1项,获第四届黑龙江省青年科技奖,获省高校教学成果一等奖和二等奖各 1项. 发表论文 70多篇,多篇被 SCI EI ISTP检索,出版著作和译著 4部.

关 琳,女,1983年生,硕士研究生,主要研究方向为演化计算、可重构计算系统.